# Dynamic Analysis of Charge Separation in Metal-Insulator-Semiconductor Devices Used for High-Power Applications

## Salman Amirzadeh

Department of Electronic Engineering, Faculty of Engineering, University of Esfahan, Esfahan, IRAN

## **Abstract**

In this study, a low-potential analysis of the charge separation dynamics in the metal-insulator-semiconductor (MIS) devices used for the architecture of the power electronic circuits, systems and networks. The separation events were supposed and analyzed at the interface regions within the bulk structures of such devices. The results of the performed analysis have shown that the charge separation may have reasonable effect on the performance and efficiency of the MIS device when the operation potentials are lower than 1 kV/m. Such potential values are the basement of the MIS power electronics employed in hyperfine electronics.

Keywords: Dynamic analysis; MIS devices; Power electronics; Charge separation

Received: 2 April 2024; Revised: 5 July 2024; Accepted: 12 July 2024; Published: 1 October 2024

## 1. Introduction

Power electronics still have their featured position in practical and industrial applications of electronics and their devices. Their efficient performance was obviously confirmed throughout their ability to produce stable and useful output [1,2]. However, the phenomena included in their performance, especially those related to the charge motion, distribution, interaction and compensation, were not intensively investigated [3,4]. Due to the inevitable existence of several surface and bulk regions within the electronic device, such phenomena should be thoroughly investigated and analyzed in order better performances and hence higher efficiencies can be achieved [5-7]. Otherwise, lower performances and efficiencies may still practical since the production economy and complexity cannot be compensated [8].

Among the most effective power electronic architectures, metal-insulator-semiconductor (MIS) devices are increasingly used and employed in modern bulk, fine and hyperfine technologies [9-13]. In case of bulk MIS devices and circuits, the phenomena of the charge motion, distribution, interaction and compensation may not be so much effective to change the performance parameters and affect the efficiencies [14,15]. Many research works and studies showed that such phenomena may cause

lower than 0.05% variations in the values of overall efficiency at potential ranges higher than 10 kV/m. This value may increase to 0.1% at extraordinary potential ranges, those are not normally practical [16]. At potential ranges lower than 1 kV/m, variations of lower than 0.01% can be observed [17-20].

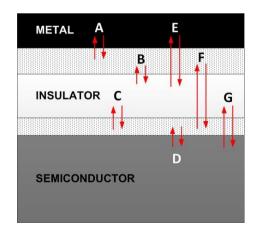

Fig. (1) Scheme of the MIS device analyzed in this study

Hyperfine technologies lead to make the variations in the performance and efficiencies relatively drastic and should be considered when the optimization of very-low-scale integration (VLSI)

1

devices, circuits, systems and networks is required [21-22]. One of the most effective phenomena is the charge separation at the interfaces within the MIS structures [23,24]. Conceptually, there can be seven different modes of charge separation within such structures, as shown in Fig. (1). Such modes can occur totally or partially at the four interface regions shown (A, B, C and D). Additionally, charge dynamic and separation events can occur thoroughly from one terminal of the structure to another without functional events in the interface region (E, F, and G). These events certainly have different rates and probabilities as they are initiated under different potential schemes and hence move between different layers [25].

In this study, a low-potential analysis of the charge separation dynamics is presented for the optimization of MIS devices used for the architecture of power electronic circuits, systems and networks.

## 2. Experiment

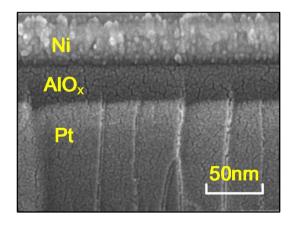

A set of MIS devices were prepared by the programmable thermal evaporation method as multilayer structures. Figure (2) shows the SEM image of the fabricated device structure. The fabricated device with the structure of Al/M/AlO<sub>x</sub>/Pt can be presented and materials of top electrode (TE) Ni and TiN, respectively. Take Al/TiN/AlO<sub>x</sub>/Pt device as an example. At first, to remove the organic and inorganic impurities, the purchased substrate comprising Pt/Ti/SiO<sub>2</sub>/Si was ultrasonically cleaned in acetone, ethanol, and DI water in sequence. The time for each ultrasonic cleaning process was 20 min. Then the 15-minute hydrophilic treatment in a vacuum with an expanded plasma cleaner (PDC-002 HARRICK PLASMA) was conducted to the cleaned Pt substrate, which enhanced the hydrophilia of the bottom electrode (BE) and made the entire spin-coating process easier to obtain.

Fig. (2) SEM image of the MIS device fabricated in this study

After the process of hydrophilic treatment, the prepared 2.5 M AlOx precursor solution was spincoated in the air onto the Pt substrate with a spin rate at 3500 rpm and the spin time was 40 s. Then the device with the structure of AlO<sub>x</sub> precursor solution/Pt was annealed at the desired temperature  $(225/250/275^{\circ}C)$  for 60 min in the air and a ~ 35 nm AlO<sub>x</sub> switching layer was grown successfully. Finally, a  $\sim 40$  nm TiN layer and a  $\sim 20$  nm Al layer were deposited onto the AlOx layer by thermal evaporator respectively. The TiN was chosen as the TE layer while the capper layer Al was used to prevent the external oxidation. The TE layer was deposited onto the switching layer through a shadow mask and a single TE was deposited with the size of 0.1 mm diameter determined by the mask aperture.

## 3. Results and Discussion

The analysis of charge separation dynamics in this study may start from the rate equations at each interface region as follows [26]:

$$R_A = \left\{ \mu_{eA} \frac{\partial \rho_e}{\partial t} + \mu_{hA} \frac{\partial \rho_h}{\partial t} \right\} \tag{1a}$$

Therrace region as follows [20]:

$$R_{A} = \left\{ \mu_{eA} \frac{\partial \rho_{e}}{\partial t} + \mu_{hA} \frac{\partial \rho_{h}}{\partial t} \right\}$$

$$R_{B} = \left\{ \mu_{eB} \frac{\partial \rho_{e}}{\partial t} + \mu_{hB} \frac{\partial \rho_{h}}{\partial t} \right\}$$

$$R_{C} = \left\{ \mu_{eC} \frac{\partial \rho_{e}}{\partial t} + \mu_{hC} \frac{\partial \rho_{h}}{\partial t} \right\}$$

$$R_{D} = \left\{ \mu_{eD} \frac{\partial \rho_{e}}{\partial t} + \mu_{hD} \frac{\partial \rho_{h}}{\partial t} \right\}$$

$$At the A interface [27]$$

$$(1a)$$

$$R_{D} = \left\{ \mu_{eD} \frac{\partial \rho_{e}}{\partial t} + \mu_{hD} \frac{\partial \rho_{h}}{\partial t} \right\}$$

$$(1d)$$

$$R_C = \left\{ \mu_{eC} \frac{\partial \rho_e}{\partial t} + \mu_{hC} \frac{\partial \rho_h}{\partial t} \right\} \tag{1c}$$

$$R_D = \left\{ \mu_{eD} \frac{\partial \rho_e}{\partial t} + \mu_{hD} \frac{\partial \rho_h}{\partial t} \right\} \tag{1d}$$

$$\lim_{\rho_h \to 0} \left( \frac{\partial \rho_h}{\partial t} \right) \approx 0$$

Therefore

$$R_A = \mu_{eA} \frac{\partial \rho_e}{\partial t}$$

(4)

At the B and C interfaces [28]

$$\rho_h < \rho_h \approx 0$$

So. (5)

$$R_B \approx 0$$

(6a)

$$R_C \approx 0$$

(6b)

$$R_C \approx 0$$

(6b)

For the E event

$$R_E = \left\{ \mu_{eE} \frac{\partial \rho_e}{\partial t} + \mu_{hE} \frac{\partial \rho_h}{\partial t} - \Gamma_E \mu_{ehE} \frac{\partial \rho_{eh}}{\partial t} \right\}$$

(7)

For the F event

For the F event

$$R_F = \left\{ \mu_{eF} \frac{\partial \rho_e}{\partial t} + \mu_{hF} \frac{\partial \rho_h}{\partial t} - \Gamma_F \mu_{ehF} \frac{\partial \rho_{eh}}{\partial t} \right\}$$

For the G event

$$R_G = \left\{ \mu_{eG} \frac{\partial \rho_e}{\partial t} + \mu_{hG} \frac{\partial \rho_h}{\partial t} - \Gamma_G \mu_{ehG} \frac{\partial \rho_{eh}}{\partial t} \right\}$$

(9)

Where  $\Gamma$  is the recombination (or decay) function, which describes the loss of charges during the dynamic event through the transient interfaces. This function can be determined experimentally at acceptable accuracy

For charges moving from the metal to the insulator through the M-I interface [29]

$$\lim_{\rho_h \to 0} \left( \frac{\partial \rho_h}{\partial t} \right) \approx 0 \tag{10}$$

$$R_E = \left\{ \mu_{eE} \frac{\partial \rho_e}{\partial t} - \Gamma_E \mu_{ehE} \frac{\partial \rho_{eh}}{\partial t} \right\} \tag{11}$$

Therefore

$$R_{E} = \left\{ \mu_{eE} \frac{\partial \rho_{e}}{\partial t} - \Gamma_{E} \mu_{ehE} \frac{\partial \rho_{eh}}{\partial t} \right\}$$

Also

$$\mu_{eE} \frac{\partial \rho_{e}}{\partial t} \gg \Gamma_{E} \mu_{ehE} \frac{\partial \rho_{eh}}{\partial t}$$

Hence

$$(11)$$

$$R_E \approx \mu_{eE} \frac{\partial \rho_e}{\partial t} \tag{13}$$

Similarly

For charges moving from the insulator to the semiconductor through the I-S interface

$$\lim_{\rho_{e} \to 0} \left( \frac{\partial \rho_{e}}{\partial t} \right) \approx 0 \tag{14}$$

Therefore

$$R_{G} = \left\{ \mu_{hG} \frac{\partial \rho_{h}}{\partial t} - \Gamma_{G} \mu_{ehG} \frac{\partial \rho_{eh}}{\partial t} \right\}$$

$$Also$$

$$R_G = \left\{ \mu_{hG} \frac{\partial \rho_h}{\partial t} - \Gamma_G \mu_{ehG} \frac{\partial \rho e_h}{\partial t} \right\}$$

(15)

$$\mu_{hG} \frac{\partial \rho_h}{\partial t} \gg \Gamma_G \mu_{ehG} \frac{\partial \rho_{eh}}{\partial t}$$

Hence

$$R_G = \mu_{hG} \frac{\partial \rho_h}{\partial t} \tag{17}$$

For charges moving through the insulator layer from metal to the semiconductor and vice versa [30]

$$\mu_{eF} \frac{\partial \rho_e}{\partial t} \approx \mu_{hF} \frac{\partial \rho_h}{\partial t} \tag{18a}$$

$$\mu_{eF} \frac{\partial \rho_e}{\partial t} \approx \mu_{hF} \frac{\partial \rho_h}{\partial t}$$

(18a)

$$\Gamma_F \mu_{ehF} \frac{\partial \rho_{eh}}{\partial t} \approx 0$$

(18b)

Therefore

R<sub>F</sub> =

$$2\mu_{eF} \frac{\partial \rho_e}{\partial t}$$

(19)

Combining all rates, we can obtain

R =

$$R_A + R_D + R_E + R_F + R_G$$

(20)

R =  $\mu_{eA} \frac{\partial \rho_e}{\partial t} + \mu_{eD} \frac{\partial \rho_e}{\partial t} + \mu_{hD} \frac{\partial \rho_h}{\partial t} + \mu_{eE} \frac{\partial \rho_e}{\partial t} + 2\mu_{eF} \frac{\partial \rho_e}{\partial t} + \mu_{hG} \frac{\partial \rho_h}{\partial t}$

$$R = 5\mu_e \frac{\partial \rho_e}{\partial t} + 2\mu_h \frac{\partial \rho_h}{\partial t} \tag{21}$$

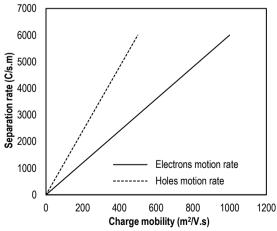

Figures (3) show the total rate of charge separation as a function of charge mobility for both types of charges existing in the MIS structure. The systematic behavior of the separation rate is not the actual situation because the charge dynamics in the MIS (and mostly all hybrid structures) are correlated due to static and dynamics electrical forces in addition to the effect of varying densities throughout the fabricated structure [31].

Fig. (3) Variation of separation rate with the charge mobility without correlation between charge dynamics

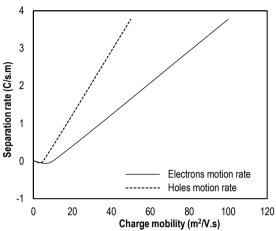

Taking the correlation between charge dynamics into account, the variation of charge separation rate with charge mobilities can be shown in Fig. (4). A kind of irregularity can be observed at the initial values of charge motion throughout the MIS structure when the potential is critically sufficient to overcome the static and dynamic forces mentioned before.

Fig. (3) Variation of separation rate with the charge mobility with correlation between charge dynamics

#### 4. Conclusion

In concluding remarks, a low-potential analysis of the charge separation dynamics in the metalinsulator-semiconductor (MIS) devices used for the architecture of the power electronic circuits, systems and networks. The separation events were supposed and analyzed at the interface regions within the bulk structures of such devices. The results of the performed analysis have shown that the charge separation may have reasonable effect on the performance and efficiency of the MIS device when the operation potentials are lower than 1 kV/m. Such potential values are the basement of the MIS power electronics employed in hyperfine electronics.

## References

- [1] M. Brzhezinskaya et al., "Large-scalable graphene oxide films with resistive switching for non-volatile memory applications", J. Alloys Comp., 849 (2020) 156699.

- A.P. Patil et al., "Tuning the analog and digital resistive switching properties of TiO2 by nanocompositing Al-doped ZnO", Mater. Sci. Semicond. Process., 115 (2020) 105110.

- T.M. Rawson et al., "Artificial intelligence can improve decision-making in management", Nat. Hum. Behav., 3(6) (2019) 543-545.

- Z. Shen et al., "Advances of RRAM Devices: [4] Resistive Switching Mechanisms, Materials and Bionic Synaptic Application", Nanomater. (Basel), 10(8) (2020) 1437.

- [5] C. Fernandez et al., "Comprehensive predictive modeling of resistive switching devices using a bias-dependent window function approach",

- Solid-State Electron., 170 (2020) 107833.

- [6] Y. Liu et al., "Effect of film thickness and temperature on the resistive switching characteristics of the Pt/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN structure", *Solid-State Electron.*, 173 (2020) 107880.

- [7] H.T. Kwon et al., "Resistive random-access memory with an a-Si/SiN<sub>x</sub> double-layer", *Solid-State Electron.*, 158 (2019) 64-69.

- [8] Y.F. Qi et al., "Resistive switching behavior of solution-processed AlO<sub>x</sub> and GO based RRAM at low temperature", *Solid-State Electron.*, 168 (2020) 107735.

- [9] R.W.a.I. Valov, "Electrochemical Reactions in Nanoionics-Towards Future Resistive Switching Memories", ECS Trans., 25(6) (2009) 431-437.

- [10] X.D. Huang et al., ""Enhancement of DC/AC resistive switching performance in AlO<sub>x</sub> memristor by two-technique bilayer approach", *Appl. Phys. Lett.*, 116(17) (2020) 73504.

- [11] Z. Shen et al., "Effect of Annealing Temperature for Ni/AlO<sub>x</sub>/Pt RRAM Devices Fabricated with Solution-Based Dielectric", *Micromach.* (*Basel*), 10() (2019) 446.

- [12] H.W. Shin and J.Y. Son, "Resistive switching characteristics of graphene/NiO/highly ordered pyrolytic graphite resistive random access memory capacitors", *J. Alloys Comp.*, 772 (2019) 900-904.

- [13] X. Kang et al., "NiO-based resistive memory devices with highly improved uniformity boosted by ionic liquid pre-treatment", *Appl. Surf. Sci.*, 480 (2019) 57-62.

- [14] H. Ryu, J. Choi and S. Kim, "Voltage Amplitude-Controlled Synaptic Plasticity from Complementary Resistive Switching in Alloying HfO<sub>x</sub> with AlO<sub>x</sub>-Based RRAM", *Metals*, 10(11) (2020) 1410.

- [15] J. Sun, J.B. Tan and T. Chen, "HfO<sub>x</sub>-Based RRAM Device With Sandwich-Like Electrode for Thermal Budget Requirement", *IEEE Trans. Electron Dev.*, 67(10) (2020) 4193-4200.

- [16] J. Kim et al., "Recent Progress of Quantum Dot □ based Photonic Devices and Systems: A Comprehensive Review of Materials, Devices, and Applications", Small Struct., 59 (2020) 1-57.

- [17] X. Hong et al., "Oxide-based RRAM materials for neuromorphic computing", *J. Mater. Sci.*, 53(12) (2018) 8720-8746.

- [18] X. Cao et al., "Enhanced Switching Ratio and Long-Term Stability of Flexible RRAM by Anchoring Polyvinylammonium on Perovskite Grains", ACS Appl. Mater. Interfac., 11(39) (2019) 35914-35923.

- [19] H. Wang and X. Yan, "Overview of Resistive

- Random Access Memory (RRAM): Materials, Filament Mechanisms, Performance Optimization, and Prospects", *phys. stat. sol.* (RRL) Rapid Res. Lett., 13(9) (2019) 1900073.

- [20] V. Gupta et al., "Resistive Random Access Memory: A Review of Device Challenges", *IETE Tech. Rev.*, 37(4) (2019) 377-390.

- [21] K. Moon et al., "RRAM-based synapse devices for neuromorphic systems", *Faraday Discuss*, 213 (2019) 421-451.

- [22] K. Bejtka et al., "TEM Nanostructural Investigation of Ag-Conductive Filaments in Polycrystalline ZnO-Based Resistive Switching Devices", ACS Appl. Mater. Interfac., 12(26) (2020) 29451-29460.

- [23] C.-C. Hsu, P.-X. Long and Y.-S. Lin, "Enhancement of Resistive Switching Characteristics of Sol-Gel TiO<sub>x</sub> RRAM Using Ag Conductive Bridges", *IEEE Trans. Electron Dev.*, (2020) 1-8.

- [24] Q. Liu et al., "Formation of multiple conductive filaments in the Cu/ZrO<sub>2</sub>:Cu/Pt device", *Appl. Phys. Lett.*, 95(2) (2009) 023501-1-023501-4.

- [25] B. Sun et al., "Effect of Cu ions assisted conductive filament on resistive switching memory behaviors in ZnFe<sub>2</sub>O<sub>4</sub>-based devices", *J. Alloys Comp.*, 694 (2017) 464-470.

- [26] M. Huang et al., "Global-gate controlled one-transistor one-digital-memristor structure for low-bit neural network", *IEEE Electron Dev. Lett.*, 10 (2020) 1-4.

- [27] X.-D. Huang et al., "Forming-Free, Fast, Uniform, and High Endurance Resistive Switching From Cryogenic to High Temperatures in W/AlO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub>/Pt Bilayer Memristor", *IEEE Electron Dev. Lett.*, 41(4) (2020) 549-552.

- [28] J. Liu et al., "Science and Technology of Integrated Super-High Dielectric Constant AlO<sub>x</sub>/TiO<sub>y</sub> Nanolaminates / Diamond for MOS Capacitors and MOSFETs", *Carbon*, 172 (2021) 112-121.

- [29] S. Yu, X. Guan and H.S.P. Wong, "On the Switching Parameter Variation of Metal Oxide RRAM—Part II: Model Corroboration and Device Design Strategy", *IEEE Trans. Electron Dev.*, 59(4) (2012) 1183-1188.

- [30] S. Liu et al., "Significant Effects of Electrode Metal Work Function on Resistive Memory Devices with Gelatin Biodielectric Layer", *J. Electrochem. Soc.*, 165(7) (2018) G90-G95.

- [31] S.M. Hong et al., "Effect of Work Function Difference Between Top and Bottom Electrodes on the Resistive Switching Properties of SiN Films", *IEEE Electron Dev. Lett.*, 34(9) (2013) 1181-1183.